The shift to 3D packaging has redefined the semiconductor landscape, but along with greater performance comes a heightened need for rigorous reliability testing. Stacked architectures introduce new variables that can undermine long-term stability if not adequately addressed. Erik Hosler, an authority in lithography and semiconductor reliability strategies, notes that testing is now as critical as design itself in ensuring these advanced chips meet the demands of real-world operation. In practice, it means reliability must be treated as a design parameter rather than an afterthought.

Reliability protocols in 3D ICs validate not only immediate performance but also endurance over years of continuous use. Stress, heat, and mechanical strain accumulate differently in stacked designs, making it essential to develop new standards of testing. Without these frameworks, the promise of 3D integration risks being undermined by hidden weaknesses that only surface late in deployment. Establishing comprehensive protocols ensures that devices can withstand both expected and unpredictable conditions across their operational lifetime.

Why Reliability Matters in 3D ICs

Reliability is the measure of whether a chip can deliver consistent performance over time. In 3D ICs, reliability is more complex because vertical stacking concentrates electrical pathways and thermal loads in smaller spaces. Failures may not appear in initial operation but emerge under prolonged stress, posing challenges for industries where downtime is costly or unacceptable.

For data centers, an unreliable chip could interrupt vast networks of servers. In consumer electronics, failures lead to shortened device lifespans and dissatisfied users. In automotive and aerospace, reliability directly impacts safety. These examples highlight why testing for endurance is not optional but a cornerstone of advanced packaging.

Stress Testing Frameworks

Stress testing in 3D ICs simulates the physical and electrical strains chips experience in operation. Voltage cycling pushes circuits to their limits, while current density evaluations reveal vulnerabilities in interconnects. By applying accelerated stress conditions, engineers can predict long-term performance in compressed timeframes.

This methodology ensures that weak points are identified before mass production. The goal is not only to expose potential defects but also to create design feedback loops. By learning how chips respond under stress, engineers refine architectures and materials for greater resilience.

Thermal Cycling and Heat Management

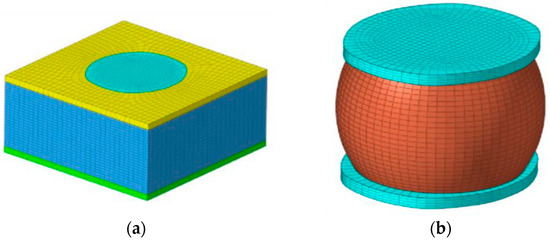

Thermal cycling is another vital protocol for 3D packages. As chips switch on and off, they expand and contract with temperature changes. In stacked architectures, these shifts are more severe because heat builds unevenly across layers. Over time, this cycling can cause microcracks, delamination, or failure in through-silicon vias.

Reliability testing subjects chips to repeated heating and cooling to replicate years of operation. By monitoring performance degradation, engineers can project how long devices will function reliably in real-world environments. This data drives improvements in thermal interface materials, packaging geometries, and cooling solutions.

Mechanical Stress and Structural Integrity

Beyond heat and voltage, 3D ICs face mechanical stress from bonding processes, packaging materials, and environmental conditions. Warping, pressure, and vibrations can weaken delicate connections between layers. Testing for structural integrity ensures that chips can endure not only controlled environments but also unpredictable real-world scenarios.

Advanced reliability protocols include bending tests, vibration analysis, and pressure simulations that replicate the physical demands chips face in automotive and aerospace sectors. These evaluations allow manufacturers to confirm that their designs can withstand not just lab conditions but the harsh realities of deployment.

The Role of Advanced Tools in Reliability Testing

Reliability testing depends heavily on advanced measurement and inspection technologies. Precision tools can detect microscopic changes in alignment, bonding strength, or material composition before they escalate into failures. Erik Hosler emphasizes, “Tools like high-harmonic generation and free-electron lasers will be at the forefront of ensuring that we can meet these challenges.”

Although his comment points to broader metrology, it applies equally to reliability testing. Without advanced inspection methods, hidden defects remain undetected until chips fail in the field. Hosler’s perspective underscores that future reliability depends not only on robust protocols but also on the sophistication of the tools we use to enforce them.

Industry Applications and Demands

Different industries apply reliability protocols with varying intensity depending on risk tolerance. In consumer electronics, the focus is on balancing cost with durability to extend product lifespans. In automotive applications, chips undergo far stricter testing to guarantee safety in high-stress conditions. Data centers emphasize thermal reliability, where chips must run continuously without degradation.

Aerospace takes reliability to its highest level, with chips tested against extreme temperatures, radiation, and vibration. Across all these sectors, the adoption of 3D packaging amplifies the demand for thorough reliability testing. The diversity of requirements demonstrates how testing protocols must be adaptable yet rigorous to address every use case.

Smarter Reliability Protocols

The future of reliability testing will involve more predictive and adaptive frameworks. Instead of relying solely on accelerated stress, testing will integrate real-time monitoring powered by embedded sensors. Chips will track their own thermal, electrical, and mechanical conditions, enabling predictive maintenance before failures occur.

Artificial intelligence will also play a role, analyzing vast datasets from reliability testing to forecast patterns of degradation with greater accuracy. It will reduce reliance on physical stress protocols and shorten testing cycles without compromising thoroughness.

Standards for 3D IC reliability will continue to develop, promoting consistency across manufacturers and industries. At the same time, sustainability goals will shape testing by reducing waste, as early fault detection prevents defective chips from advancing through expensive production steps.

Building Confidence in the Future of 3D Integration

Reliability testing is the safeguard that ensures 3D packaging delivers more than just theoretical performance. By exposing chips to stress, thermal cycling, and mechanical strain, engineers confirm that advanced designs can endure years of real-world operation.

With precision tools and more innovative protocols, reliability becomes not just a checkbox but a competitive advantage. Companies that master these practices will deliver chips that inspire Confidence across industries, from mobile devices to mission-critical aerospace systems.

As 3D integration pushes density and complexity higher, reliability testing assures that progress will be sustainable. In shaping the next generation of chips, endurance is not assumed, but proven. This commitment to validation transforms innovation from possibility into trust, ensuring that advanced designs can meet the demands of real-world deployment.